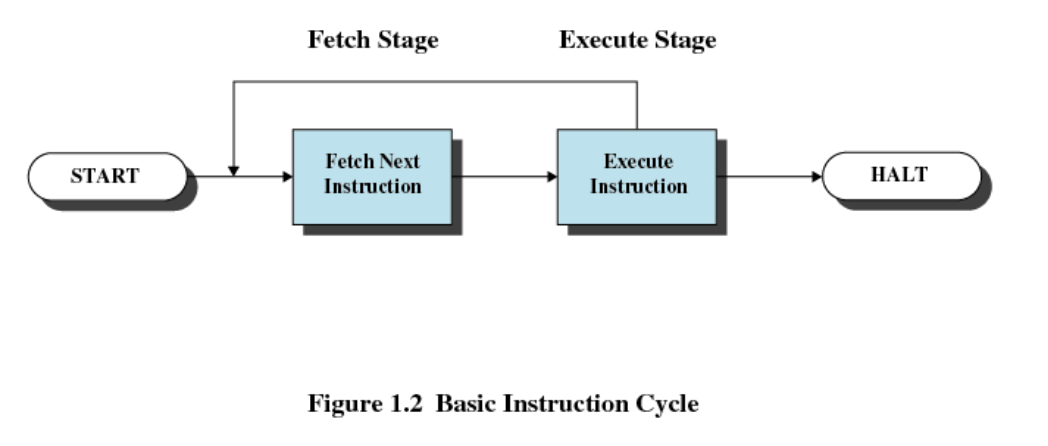

Basic Elements

- Processor (CPU)

- Main Memory (RAM)

- 휘발성 메모리

- real/primary memory 라고도 부름

- System bus

- CPU, 메모리, IO 모듈 간 데이터 전달 통로

- Data Bus, Address Bus, Control Bus 등

- I/O modules

- 하드디스크, 키보드, 네트워크 등과 연결된 외부 장치와의 인터페이스

- 보조적인 메모리 장치

- 통신(데이터 입출력) 장치

CPU의 구성

CPU를 구성하는 컴포넌트

- ALU(Arithmetic Logic Unit): 계산 담당

- CU(Control Unit): CPU 제어

- Register: 데이터 저장

Processor Registers

- Control and Status Registers

- PC(Program Counter): 다음에 실행할 명령어의 주소를 저장

- IR(Instruction Register): 방금 Fetch(가져온) 명령어를 저장

- PSW(Program Status Word): CPU의 상태를 요약해서 담고 있음

- Condition Codes (조건 코드): ALU 연산 결과를 바탕으로 설정되는 상태 플래그

- 조건 연산(if, for, while…) 등에서 사용

- Zero Flag(Z) - 연산 결과가 0일때

- Negative Flag(N) - 연산 결과가 음수일 때

- Overflow Flag(V) - 부호 있는 연산에서 오버플로우 발생했을 때

- Carry Flag(C) - 무부호 연산에서 자리 올림/내림이 발생했을 때

- Interrupt enable/disable

- Interrupt 받을 수 있는지, 무시할지 설정

- Mode Bit

- User Mode(사용자 모드): 사용자 프로세스 실행 중일 때(하드웨어 접근 제한)

- Supervisor/Kernel Mode: 운영체제가 실행 중일 때

- Condition Codes (조건 코드): ALU 연산 결과를 바탕으로 설정되는 상태 플래그

- User-visible registers

- 어셈블리어나 머신어셈블리 수준에서 프로그래머가 직접 접근 가능

- Registers for Data I/O

- MAR(Memory Address Register): 다음 Read(LOAD)나 Write(STORE)할 메모리 주소를 명시

- MBR(Memory Buffer Register): STORE & WRITE

- STORE: 메모리에 쓸 데이터를 저장

- LOAD: 메모리에서 읽어온 데이터 저장

- I/O Adress Register, I/O Buffer Register

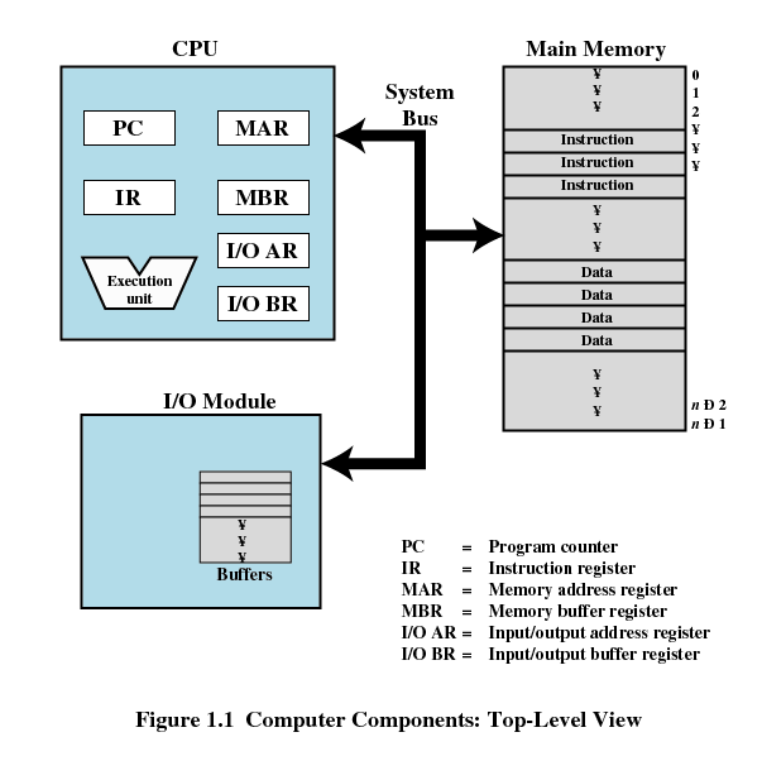

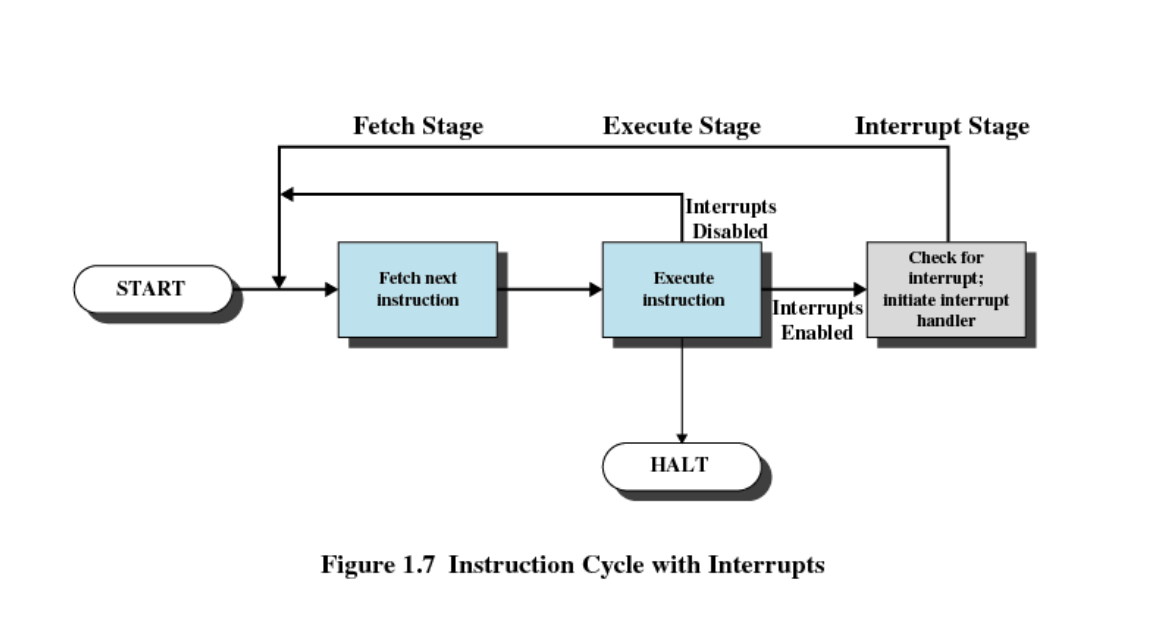

Instruction Execution

명령어 수행은 두 단계로 이루어진다.

- Fetch Stage

- CPU는 PC에 저장된 주소를 따라 메모리에서 명령어를 읽어옴

- 읽어온 명령어는 IR에 저장

- Fetch 이후 PC는 Increment 됨

- Execute Stage

- IR에 저정된 명령어를 실행

Instruction Categories (명령어 유형)

유형 설명 Processor-Memory (프로세서-메모리) 레지스터와 메모리 사이의 데이터 이동 Processor-I/O (프로세서-I/O) CPU와 I/O 장치 간 데이터 전송 Data Processing (데이터 처리) 산술, 논리 연산 수행 Control (제어 명령어) 프로그램 흐름 제어 (분기, 점프 등)

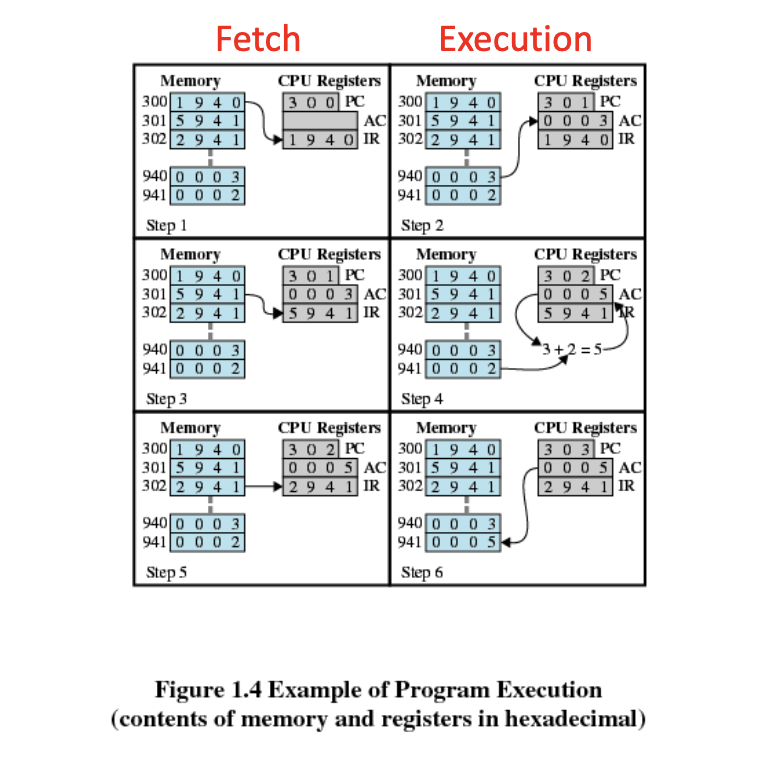

Example of Program Execution

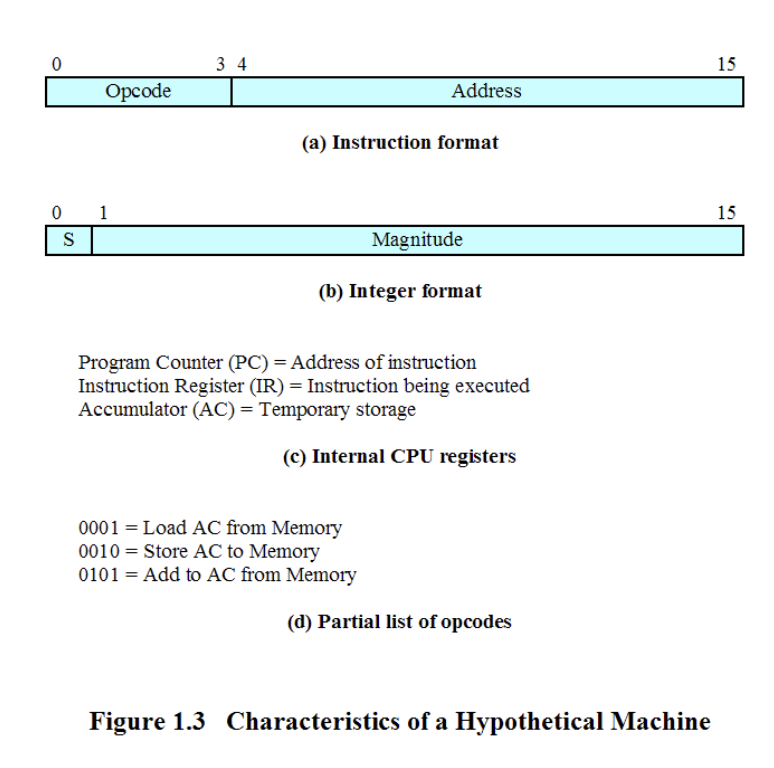

Opcode (Operation Code): CPU가 수행할 연산을 지정 (연산 코드, ISA에 정의되어 있음)

- Fetch (Step1)

- (PC에 저장된) Memory의

300주소에 있는1940Instruction을 IR에 저장 - PC Increment (

301)

- (PC에 저장된) Memory의

- Execution (Step1)

- IR에 있는 Instruction 수행

- Opcode 1(Load Ac from Memory) 연산임

- Memory

940주소에 있는0003Data를 AC에 저장

- Fetch (Step2)

- Memory의

301주소에 있는5941Instruction을 IR에 저장 - PC Increment (

302)

- Memory의

- Execution (Step2)

- IR에 있는 Instruction 수행

- Opcode 5(Add to AC from Memory) 연산임

- Memory

941에 있는0002Data를 AC의0003데이터와 덧셈을 수행하여 결과0005를 AC에 저장

- Fetch (Step3)

- Memory의

302주소에 있는2941Instruction을 IR에 저장 - PC Increment (

303)

- Memory의

- Execution (Step3)

- IR에 있는 Instruction 수행

- Opcode 2(Store AC to Memory) 연산임

- Memory

942주소에 AC의 값0005를 저장

Interrupt

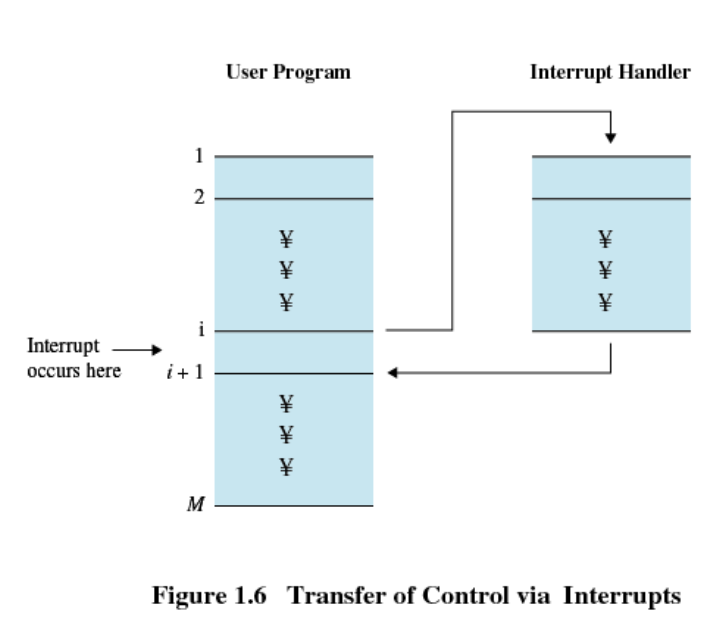

Interrupt & Interrupt Handler

대부분의 I/O 장치는 프로세서보다 느림. 프로세서가 I/O를 기다리면서 대기하는 것은 비효율적이다.

Interrupt란 CPU가 실행 중인 프로그램을 잠시 멈추고,

긴급하거나 중요한 이벤트를 처리하기 위해 다른 프로그램(Interrupt Handler)를 실행하는 메커니즘

Interrupt Cycle

- 현재 작업 중이던 프로그램 상태(PC, PSW 등)를 저장

- Interrupt Handler로 Jump

- Interrupt Handler의 코드 수행

- 저장했던 상태를 복원하고 원래 프로그램으로 복귀

Interrupts Enabled/Disabled 상태는 위에서 다룬 PSW Register에 저장되어 있음

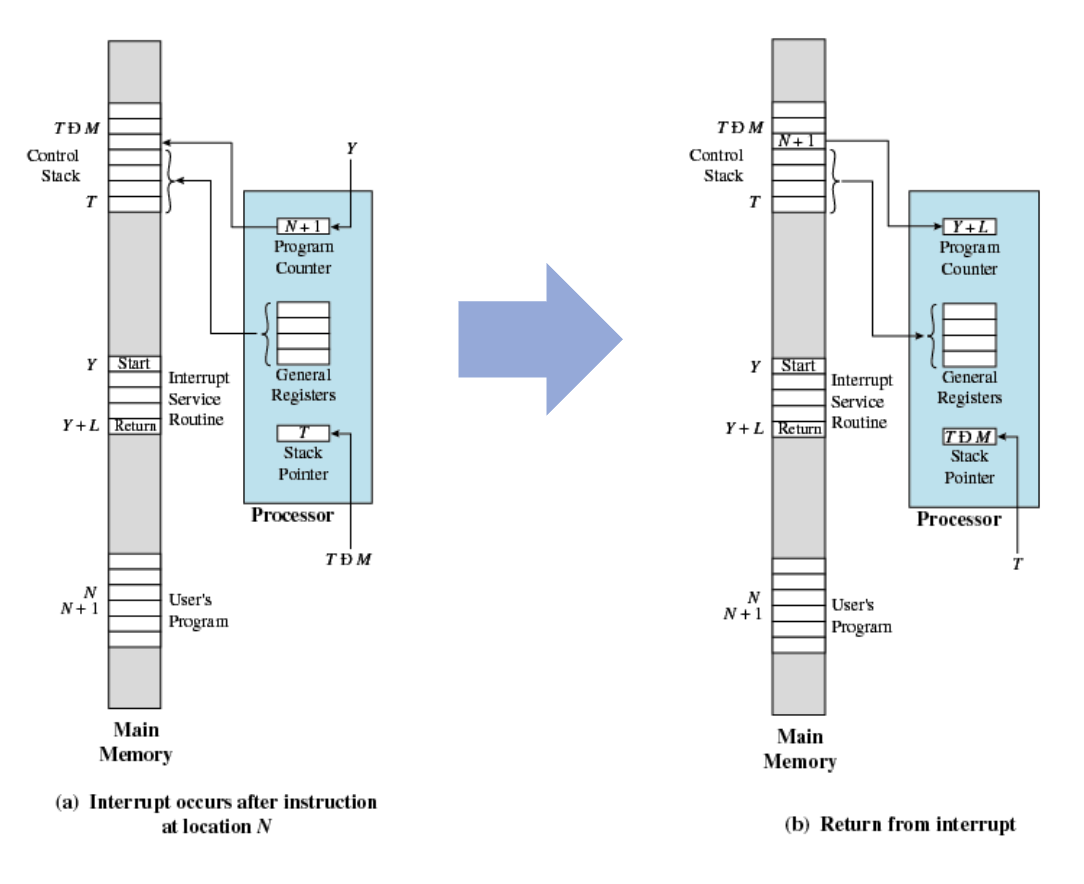

Changes in Memory and Registers for an Interrupt

- Instruction N이 실행된 이후 Inturrupt 발생

- Stack Pointer에서 가르키는

T부터 Control Stack에 General Registers와 PC의 상태 저장(T - M까지) - Program Counter에

Y(Interrupt Handler의 시작 주소)저장 Y~Y + L(Intterupt Service Routine) 수행- Control Stack의 상태 Pop하며 PC와 General Register 상태 복구(Restore)

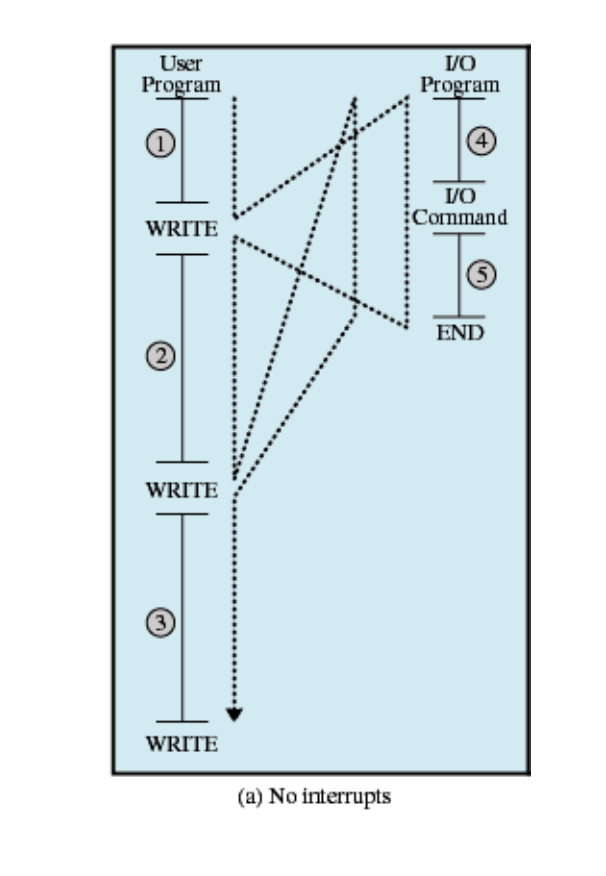

Program Flow of Control

Without Interrupts

WRITE: I/O 쓰기 System Call 예시

프로그램이 I/O 명령을 내리고, I/O가 끝날 때까지 계속 대기(비효율적)

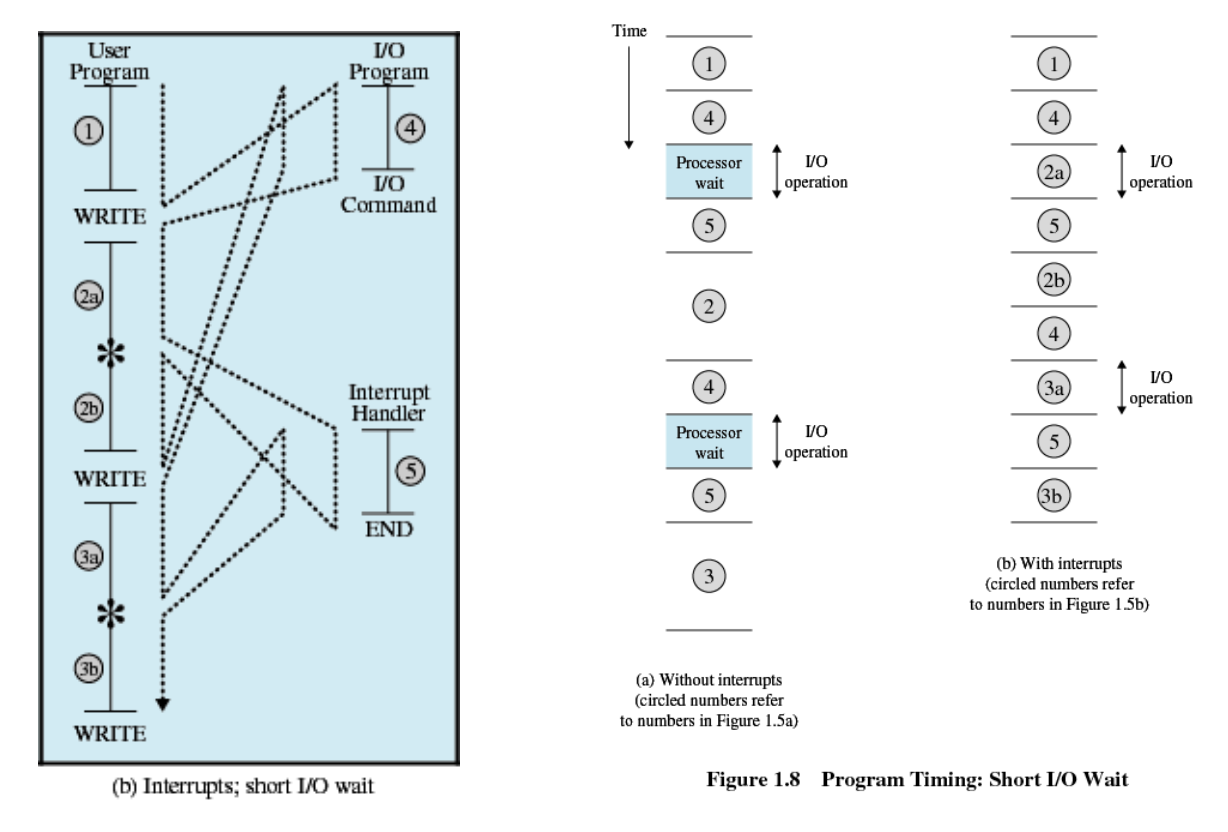

With Interrupts: Short I/O Wait

프로그램이 I/O 명령을 내리고, User Program에 복귀한다.

I/O 작업 시간 동안 프로세서가 작업(2a, 3a)을 수행하여 효율적으로 사용됨.

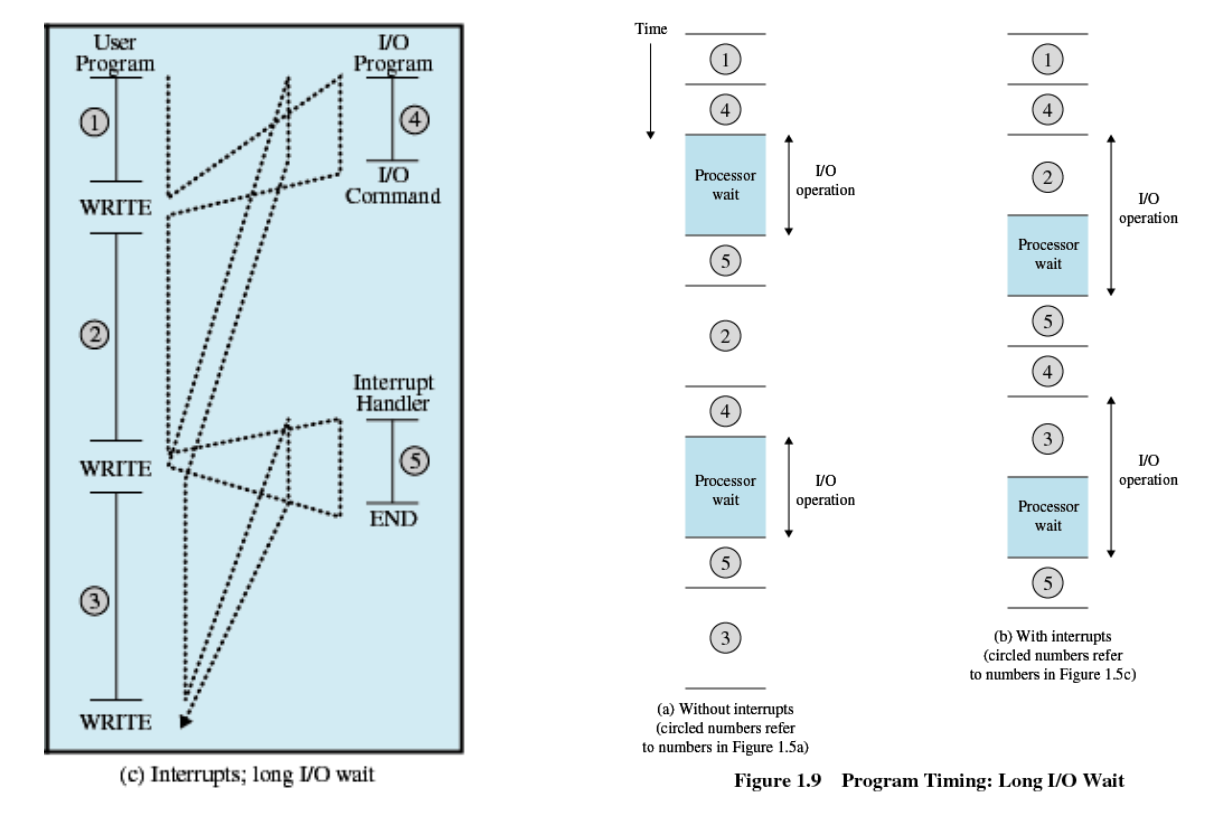

With Interrupts: Long I/O Wait

위의 경우는 Short I/O이기에 가능,

Long I/O의 경우 작업 2(2a, 2b)가 모두 수행될 동안 I/O 작업이 끝나지 않을 수 있음.

I/O 명령은 순서가 보장되어야할 필요가 있음 (원칙적으로는, Disk Scheduling 등의 예외가 있다고 함)

그래서 (b)와 같이 Long I/O의 경우, I/O 동작의 순서를 지키기 위해 Processor Wait이 발생할 수 있음.

Multiprogramming

위에서 본 것처럼 Interrupt를 사용하더라도, 프로세서가 효율적으로 사용되지 않을 수 있다.

이 상황처럼, 한 프로그램이 I/O 대기 상태에 들어갈 때의 상황에서 다른 프로그램을 대신 실행하는 방식으로 프로세서의 효율성을 극대화 시키는.방식이 Multiprogramming이다.

CPU가 여러 개의 프로그램을 동시에 실행하는 것처럼 보이도록 실행 순서를 빠르게 전환하며 처리하는 방식.

따라서 Multiprogramming에서는 Interrupt Handler가 끝나도 원래 실행하던 프로그램으로 돌아가지 않을 수 있다.

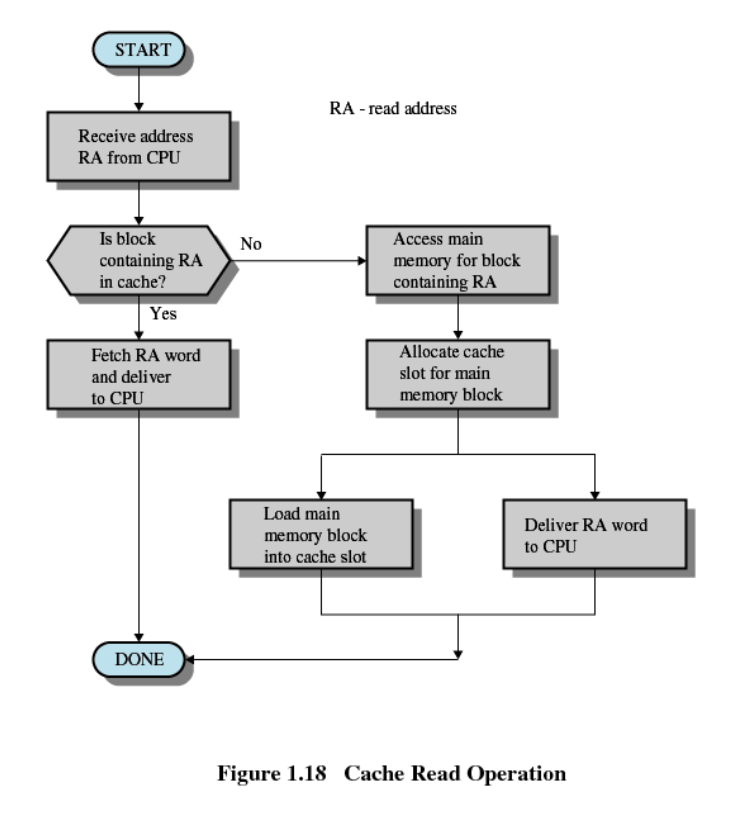

Cache Memory

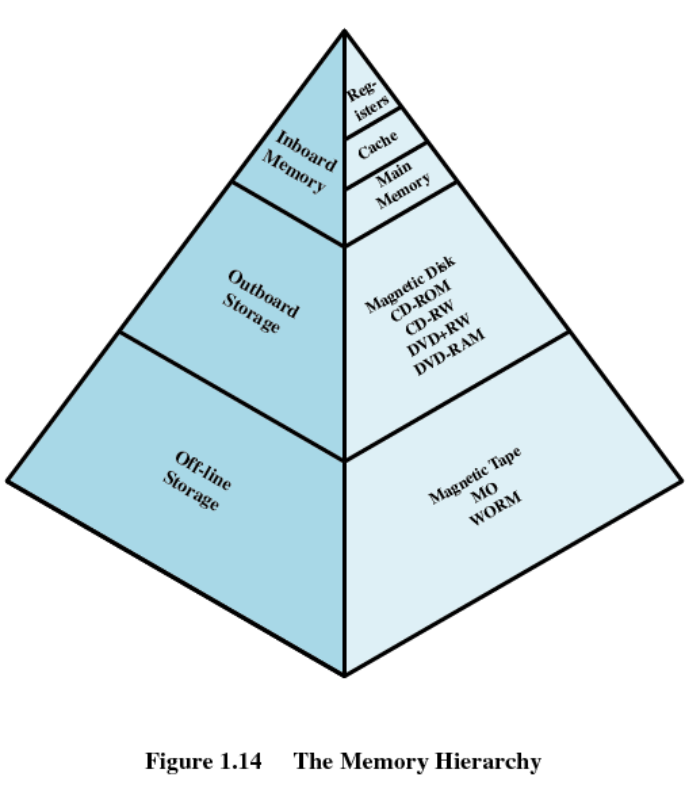

Memory Hierarchy

저장장치의 속도, 용량, 비용은 트레이드오프 관계임

여러 종류의 메모리를 계층적으로 구성해서 성능과 비용을 모두 만족시키는 구조를 사용할 수 있다.

상위 계층에 있을수록 속도가 빠르고, 용량이 작으며, 단가가 비싸다.

Locality of Reference

참조의 지역성

프로그램은 최근에 참조한 데이터나 가까운 주소의 데이터를 다시 참조하는 경향이 있다.

따라서 상위 계층 메모리에 이런 데이터를 캐싱해두는 방식으로 효율성을 극대화할 수 있으며 이런 데이터 이동의 관리는 운영체제의 역할이다.

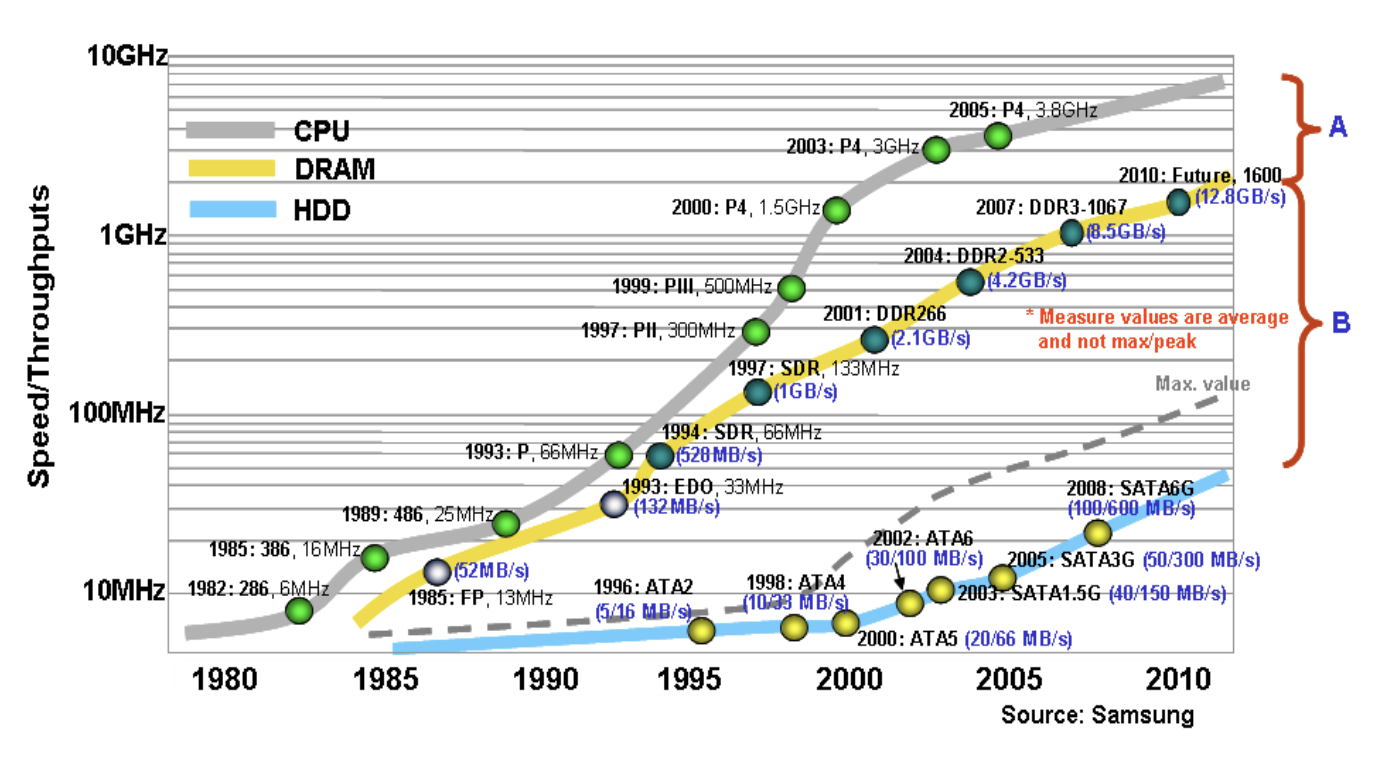

CPU / DRAM / HDD Speed

A > B 이다 (로그 스케일임), CPU 입장에서는 DRAM 속도도 너무 느림.

DRAM과 CPU 사이의 속도 차이를 줄이기 위해 Cache Memory가 만들어짐.

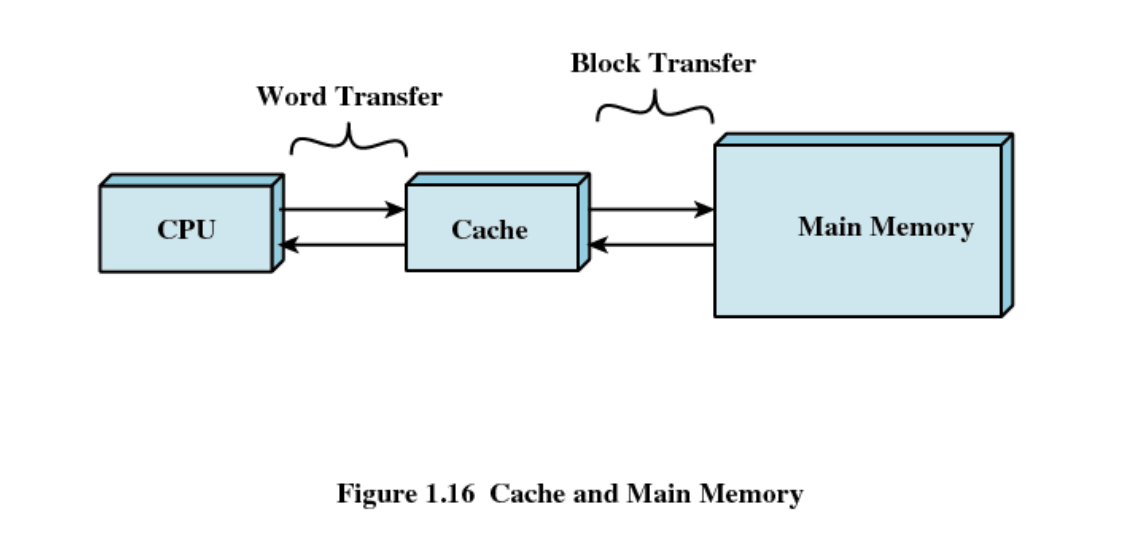

Cache Memory

CPU와 메인 메모리(RAM) 사이에 위치한 소형 고속 메모리

DRAM보다 훨씬 빠른 SRAM을 사용함

Cache Design

| 요소 | 설명 |

|---|---|

| Cache Size (캐시 크기) | 너무 작으면 자주 Miss, 너무 크면 비싸고 느려짐 |

| Block Size (블록 크기) | 한 번에 캐시에 저장하는 단위 너무 크면, 인기 없는 데이터까지 저장될 수도 있음 |

| Mapping Function (매핑 함수) | 메모리 주소 → 캐시 위치 지정 방식 |

| Replacement Algorithm (교체 알고리즘) | 새 데이터가 들어올 때 어떤 블록을 뺄지 결정 (예: LRU - Least Recently Used) |

| Write Policy (쓰기 정책) | 캐시에서 변경된 데이터를 메모리에 언제 쓸지 |

Special Instructions for Cache Bypass

Non-temporal LOAD/STORE = 캐시를 우회하도록 명시하는 명령

- 큰 배열이나 멀티미디어 파일 등은 연속적으로 접근되고, 캐시에 넣어봤자 다시 안 쓰이는 경우가 많음 (Sequential Flooding 발생할 수도)

- 이런 경우 캐시를 우회해서 오히려 성능을 높일 수 있음

Disk Cache

Disk Cache는 하드 디스크와 메인 메모리 사이에 위치한다.

Disk I/O 속도를 높이기 위해 메모리의 일부분을 디스크용 캐시 버퍼로 사용한다.

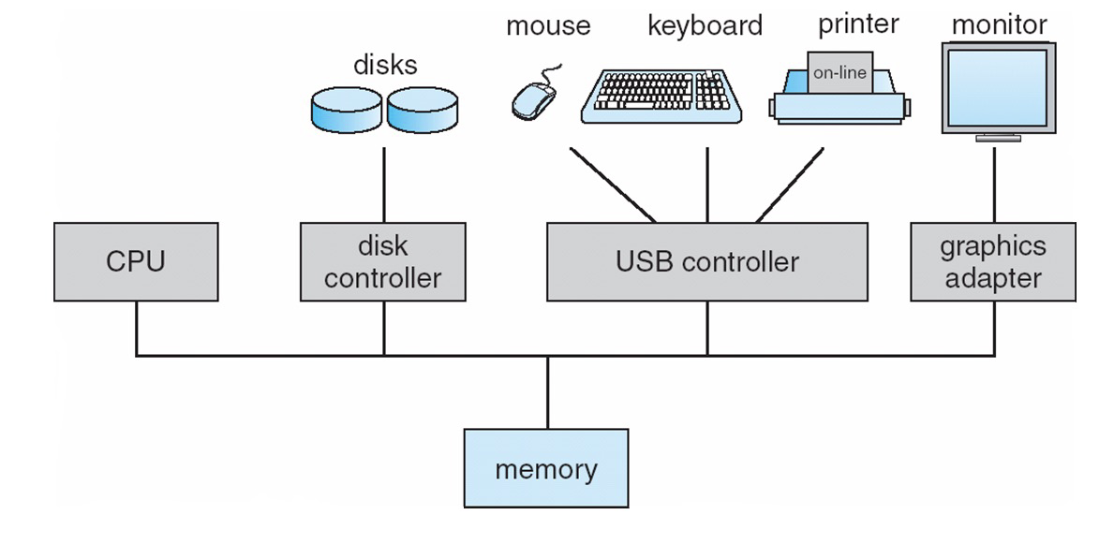

Computer System Operation

- CPU, Main Memory, I/O Device Controllers가 공통 Bus를 통해 연결되어 있음

- CPU와 I/O 장치는 동시에 실행 가능함 (병행 실행)

- I/O 장치는 각각 Device Controller (장치 제어기)를 가짐

- 이들은 로컬 버퍼(local buffer)를 가짐

- 데이터는 메모리 ↔ 버퍼 ↔ I/O 장치 순으로 이동

- Device Controller는 I/O가 완료(데이터를 버퍼에 올려놓으면)되면 Interrupt를 발생시켜 CPU에 알림

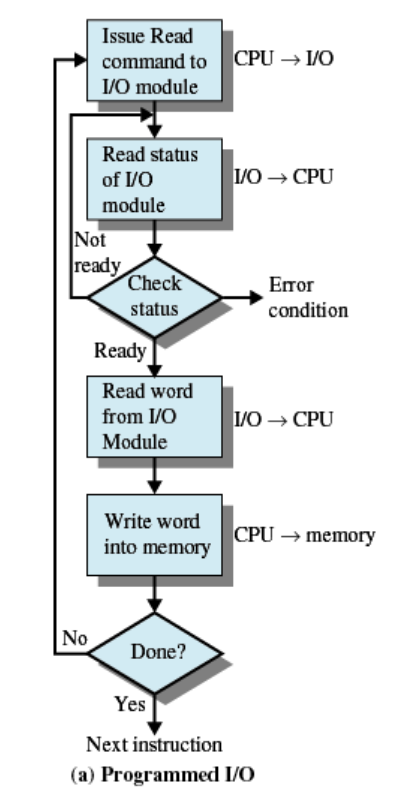

I/O 처리 방식의 비교

운영체제는 I/O 요청을 처리할 때, 다음 세 가지 방식 중 하나를 사용한다.

Programmed I/O

CPU가 I/O 장치 상태를 Polling(직접 계속 검사) 하면서 데이터 전송

- CPU가 I/O가 끝났는지 반복해서 확인해야 함

- 모든 과정에 CPU가 관여하며, I/O에 완전히 종속됨

- Interrupt 는 발생하지 않음

매우 비효율적임

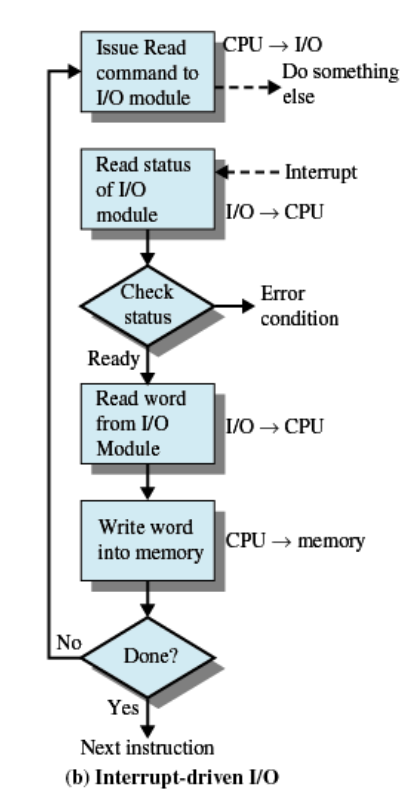

Interrupt-Driven I/O

I/O 장치가 준비되면 CPU에게 Interrupt를 발생시키고 CPU는 처리 루틴 실행

- CPU가 다른 일 하다가 필요할 때만 처리

- 데이터의 전송은 여전히 CPU가 관여

- 데이터가 한 Word씩 CPU를 거쳐서 이동한다

Programmed I/O보다 낫지만, CPU 자원 낭비 여전히 존재함

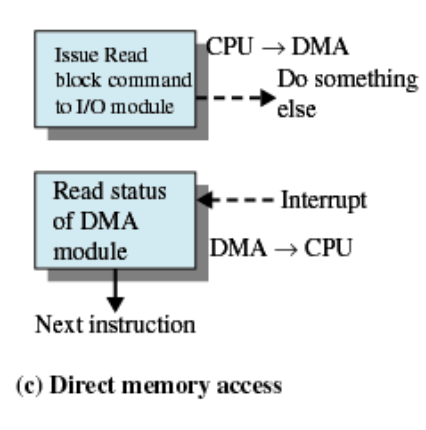

Direct Memory Access (DMA)

I/O 장치가 CPU의 개입 없이 메모리와 직접 블록 단위 전송 수행

- CPU는 시작 요청만 하고, 나중에 완료되면 Interrupt로 알림만 받음

DMA Controller

DMA Controller: I/O 장치와 메모리 간의 데이터 전송을 관리해주는 전용 하드웨어

DMA Controller가 정확히 제한된 권한 내에서 I/O의 메모리 접근을 제어한다.

- CPU가 DMA Controller에 명령을 전달

- 시작 주소 (메모리 위치), 전송할 데이터의 크기 등

- DMA Controller가 I/O ↔ 메모리 간 직접 데이터 전송 수행

- 이때 버스 제어권도 잠시 CPU에서 DMA로 넘어감 (Bus Arbitration)

- CPU는 이 동안 다른 작업 수행 가능

- 전송 완료 후 인터럽트를 CPU에 보냄

Computer Startup

- Bootstrap Program

- 컴퓨터가 켜졌을 때 가장 먼저 실행되는 코드

- ROM / EPROM에 저장되어 있음 (전원을 꺼도 사라지지 않는 비휘발성 메모리임)

- 운영체제를 메모리에 적재하고 실행함